March 2003

M9011 Electronic Ignition Interface

## LM9011 Electronic Ignition Interface General Description

The LM9011 is an interface circuit which integrates the timing detection and logic control functions required for an automotive electronic ignition system into one device.

A VRS interface is provided for crankshaft position information via a toothed-wheel.

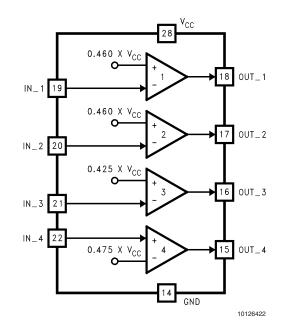

Four voltage comparators are provided for hardware diagnostics.

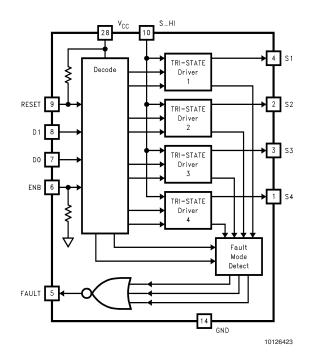

An electronic timing interface with output fault diagnostics is provided to enable a micro-processor to drive an external four channel ignition spark circuit.

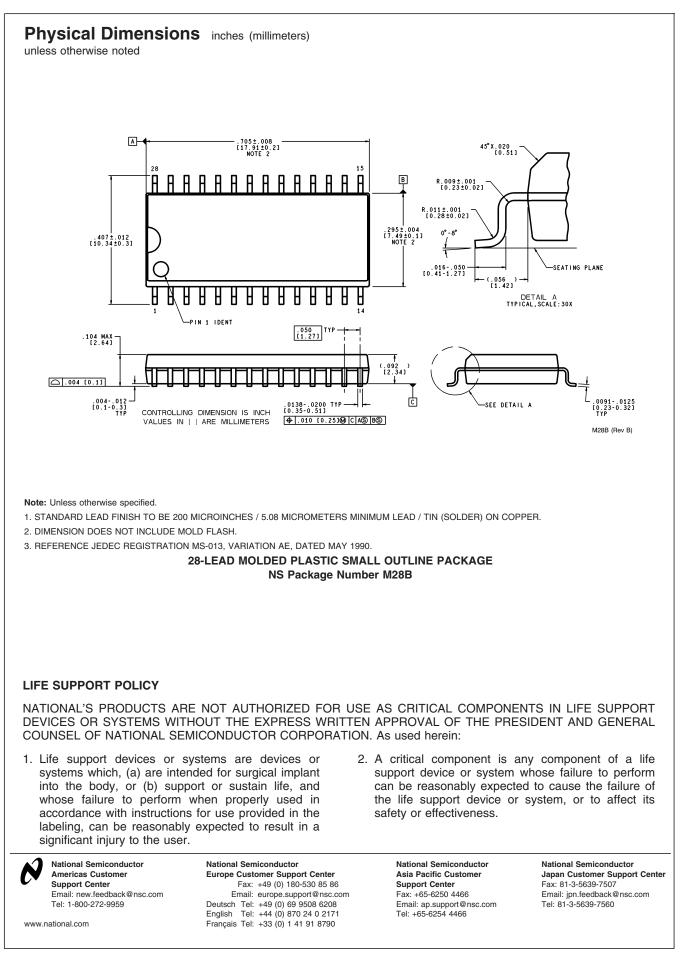

The LM9011 is fully specified over the automotive temperature range of -40°C to +125°C, and is available in a 28 pin Small Outline surface mount package.

## **Key Specifications**

#### **Features**

- Single 5V supply operation

- VR Sensor Interface with dynamic hysteresis

- Four Channel Electronic Timing spark driver with output diagnostics

- Electronic Timing Interface spark driver output voltage from 5V to 16V

- One Non-Inverting voltage comparator with hysteresis

- Three Inverting voltage comparators with hysteresis

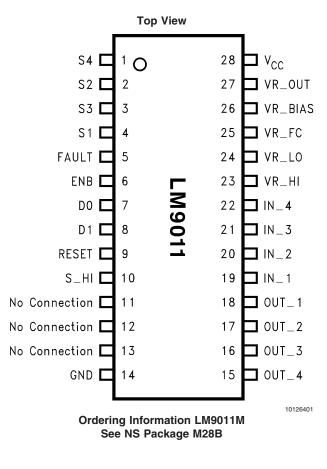

## **Connection Diagram**

## Absolute Maximum Ratings (Note 1)

| Voltage                      | -0.3V to +7.0V  |

|------------------------------|-----------------|

| S_HI Voltage                 | -0.3V to 26.5V  |

| VR_HI and VR_LO Inputs       | +/-3mA          |

| Comparator Inputs            | -0.3V to +7.0V  |

| Timing Interface Inputs      | -0.3V to +7.0V  |

| ESD Susceptibility (Note 3)  | +/-2000V        |

| Maximum Junction Temperature | 150°C           |

| Storage Temperature Range    | -65°C to +150°C |

| Lead Soldering Information:  |                 |

| Vapor Phase (60 Seconds)     | 215°C           |

| Infrared (15 Seconds)        | 220°C           |

|                              |                 |

## **Operating Ratings** (Note 3)

| V <sub>CC</sub> Voltage             | 4.75V to 5.25V                 |

|-------------------------------------|--------------------------------|

| S_HI Voltage                        | V <sub>CC</sub> to 26V         |

| Sx Outputs                          | -0.3V to S_HI +0.3V            |

| Comparator Inputs                   | -0.3V to V <sub>CC</sub> +0.3V |

| VR_HI and VR_LO Inputs              | +/-2.75mA                      |

| Timing Interface Inputs             | -0.3V to V <sub>CC</sub> +0.3V |

| Thermal Resistances (M28B):         |                                |

| Junction to Case (0J-C)             | 15°C/W                         |

| Junction to Ambient ( $\theta$ J-C) | 69°C/W                         |

|                                     |                                |

**DC Electrical Characteristics** The following specifications apply for  $V_{CC} = 5V$ ,  $V_{RESET} = V_{CC}$ ,  $V_{S_{HI}} = V_{CC}$ , -40°C  $\leq T_A \leq +125$ °C, Application Circuit Figure 16, unless otherwise specified.

| Symbol             | Parameter                                  | Conditions                                                                                         | Minimum                 | Maximum                 | Units    |

|--------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------|-------------------------|-------------------------|----------|

|                    |                                            | RESET, $IN_4 = V_{CC}$                                                                             |                         |                         |          |

|                    |                                            | ENB, D0, D1, IN_1, IN_2, IN_3 =                                                                    | 1                       |                         |          |

| I cc               | Supply Current                             | ov                                                                                                 |                         | 25                      | mA       |

|                    |                                            | VR_HI = +12.5µA                                                                                    |                         |                         |          |

|                    |                                            | VR_LO = -12.5µA                                                                                    | 1                       |                         |          |

| Comparat           | ors                                        |                                                                                                    |                         |                         |          |

| V <sub>TH</sub> 1  | Input Threshold                            | $V_{IN}$ _1 Decreasing from $V_{CC}$ to 0V<br>until $V_{OUT}$ 1 > $V_{CC}/2$                       | V <sub>CC</sub> X 0.435 | V <sub>CC</sub> X 0.485 | V        |

| V <sub>TH</sub> 2  | Input Threshold                            | $V_{IN}$ 2 Decreasing from $V_{CC}$ to 0V<br>until $V_{OUT}$ 2 > $V_{CC}$ /2                       | V <sub>CC</sub> X 0.435 | V <sub>CC</sub> X 0.485 | V        |

| V <sub>TH</sub> 3  | Input Threshold                            | $V_{IN_3}$ Decreasing from $V_{CC}$ to 0V<br>until $V_{OUT_3} > V_{CC}/2$                          | V <sub>CC</sub> X 0.40  | V <sub>CC</sub> X 0.45  | V        |

| $V_{TH}4$          | Input Threshold                            | $V_{IN}4$ Decreasing from $V_{CC}$ to 0V<br>until $V_{OUT}4 < V_{CC}/2$                            | V <sub>CC</sub> X 0.45  | V <sub>CC</sub> X 0.50  | V        |

| V <sub>HYST</sub>  | Input Hysteresis                           | All Comparators                                                                                    | 150                     | 400                     | mV       |

| I <sub>BIAS</sub>  | Input Bias Current                         | $      IN_1, IN_2, IN_3 = 0V \le V_{IN} \le V_{CC} \\       IN_4 = 0V \le V_{IN} \le V_{CC} - 1V $ |                         | 750                     | μA       |

| V <sub>OH</sub>    | Output High Voltage                        | $I_{LOAD} = -100 \mu AV$ $V_{CC} - 1$                                                              |                         |                         | V        |

| V <sub>OL</sub>    | Output Low Voltage                         | $I_{LOAD} = +100 \mu AV$                                                                           |                         | 750                     | mV       |

| VR Senso           | r Interface                                |                                                                                                    |                         |                         |          |

| V <sub>OH</sub>    | Output High Voltage                        | I <sub>LOAD</sub> = -15μΑ<br>VR_HI= -1mA, VR_LO = +1mA                                             | V <sub>cc</sub> -1      |                         | V        |

| V <sub>OL</sub>    | Output Low Voltage                         | Load = +15µA<br>VR_HI=+1mA, VR_LO = -1mA                                                           |                         | 750                     | mV       |

|                    | Minimum Detect Differential Input          | $-40^{\circ}C \le T_A \le +25^{\circ}C$                                                            | 0.5                     | 3.0                     | uA Pk-Pk |

| IDIFF(MIN)         |                                            | T <sub>A</sub> = +85°C (Note 5)                                                                    | 0.6                     | 3.5                     | uA Pk-Pk |

|                    | Current (Note 4)                           | T <sub>A</sub> = +125°C                                                                            | 1.0                     | 5.0                     | uA Pk-Pk |

| I <sub>HYS</sub> 1 | Input Hysteresis (Note 4)                  | I <sub>DIFF</sub> = 1mA pk-pk                                                                      | 75                      | 250                     | uA Pk    |

| I <sub>HYS</sub> 2 | Input Hysteresis (Note 4)                  | I <sub>DIFF</sub> = 2.5mA pk-pk                                                                    | 185                     | 625                     | uA Pk    |

|                    | Timing Interface                           |                                                                                                    |                         | · 1                     |          |

| V <sub>IH</sub>    | Input Logic 1 D0, D1, ENB, RESET           |                                                                                                    | V <sub>CC</sub> X 0.7   |                         | V        |

| V <sub>IL</sub>    | Input Logic 0 D0, D1, ENB, RESET           |                                                                                                    |                         | V <sub>CC</sub> X 0.3   | V        |

| I <sub>IH</sub>    | Input High Current Inputs D0, D1,<br>RESET | $V_{IN} = V_{CC}$                                                                                  |                         | 10                      | μΑ       |

| I <sub>IH</sub>    | Input High Current Input ENB               | $V_{IN} = V_{CC}$                                                                                  |                         | 125                     | μA       |

| <b>DC Electrical Characteristics</b> The following specifications apply for $V_{CC} = 5V$ , $V_{RESET} = V_{CC}$ , $V_{S_{HI}} = V_{CC}$ , |

|--------------------------------------------------------------------------------------------------------------------------------------------|

| -40°C $\leq$ T <sub>A</sub> $\leq$ +125°C, Application Circuit Figure 16, unless otherwise specified. (Continued)                          |

| Symbol                                                              | Parameter                                          | Conditions                                                                    | Minimum               | Maximum               | Units |  |

|---------------------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------------------------------|-----------------------|-----------------------|-------|--|

| I                                                                   | Input Low Current Inputs D0, D1,<br>ENB            | V <sub>IN</sub> = 0V                                                          |                       | -10                   | μA    |  |

| I <sub>IL</sub>                                                     | Input Low Current Input RESET                      | $V_{IN} = 0V$                                                                 |                       | -125                  | μA    |  |

| V <sub>OH</sub>                                                     | Output High Voltage Outputs S1,<br>S2, S3, S4      | $I_{LOAD} = -10mA, V_{S_{HI}} = 5V$ 3.75<br>$I_{LOAD} = 1mA, V_{S_{HI}} = 5V$ |                       |                       | V     |  |

| V <sub>OL</sub>                                                     | Output Low Voltage Outputs S1,<br>S2, S3, S4       |                                                                               |                       | 300                   | mV    |  |

| V <sub>OH</sub>                                                     | Output High Voltage Outputs S1,<br>S2, S3, S4      | I <sub>LOAD</sub> = -10mA, V <sub>S_HI</sub> = 16V                            | 14                    |                       | V     |  |

| V <sub>OL</sub>                                                     | Output Low Voltage Outputs S1,<br>S2, S3, S4       | $I_{LOAD} = 1$ mA, $V_{S_{HI}} = 16V$                                         |                       | 450                   | mV    |  |

| V <sub>OH</sub>                                                     | Output High Voltage Outputs S1,<br>S2, S3, S4      | $I_{LOAD} = -10mA, V_{S_HI} = 26V$                                            | 22                    |                       | V     |  |

| V <sub>OL</sub>                                                     | Output Low Voltage Outputs S1,<br>S2, S3, S4       | $I_{LOAD} = 1$ mA, $V_{S_{HI}} = 26V$                                         |                       | 600                   | mV    |  |

| V <sub>OH</sub>                                                     | FAULT Pin Output High Voltage                      | I <sub>FAULT</sub> = -100μA, no fault                                         | V <sub>cc</sub> -1    |                       | V     |  |

| V <sub>OL</sub>                                                     | FAULT Pin Output Low Voltage                       | I <sub>FAULT</sub> = 100μA, any fault                                         |                       | 750                   | mV    |  |

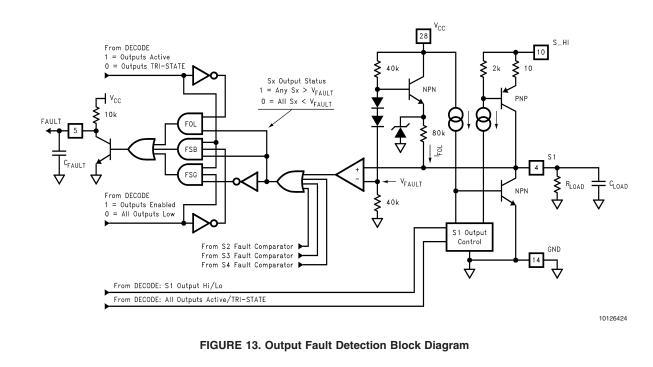

| V <sub>FAULT</sub> Fault Treshold Voltage Outputs S1,<br>S2, S3, S4 |                                                    | Sx Output Short Fault                                                         | V <sub>CC</sub> X 0.2 | V <sub>CC</sub> X 0.5 | V     |  |

| I <sub>FOL</sub>                                                    | TRI-STATE Output Current Outputs<br>S1, S2, S3, S4 | $V_{RESET} = 0V, V_{S _HI} = 5V$<br>$R_{LOAD} = 10K\Omega$                    | -12                   | -50                   | μA    |  |

## **AC Electrical Characteristics**

The following specifications apply for  $V_{CC} = 5V$ ,  $V_{S_{HI}} = V_{CC}$ ,  $V_{RESET} = V_{CC}$ ,  $-40^{\circ}C \le T_A \le +125^{\circ}C$ . The AC Timing Characteristics are not production tested. Minimum and Maximum limits are guaranteed by device characterization.

| Symbol              | Parameter                         | Conditions                                                                | Minimum | Maximum                                  | Units |

|---------------------|-----------------------------------|---------------------------------------------------------------------------|---------|------------------------------------------|-------|

| Comparat            | tors                              | · · · · · ·                                                               |         | L. L |       |

| T <sub>RISE</sub>   | Output Rise Time                  | 10% to 90%, C <sub>LOAD</sub> = 25pF                                      |         | 5                                        | μs    |

| T <sub>FALL</sub>   | Output Fall Time                  | 90% to10%, C <sub>LOAD</sub> = 25pF                                       |         | 5                                        | μs    |

| VR Sensc            | r Interface (Note 4)              |                                                                           |         |                                          |       |

| T <sub>RISE</sub>   | Output Rise Time                  | 10% to 90%, $C_{LOAD}$ = 100pF,<br>$R_{LOAD}$ = 100K $\Omega$             |         | 10                                       | μs    |

| T <sub>FALL</sub>   | Output Fall Time                  | 90% to10%, $C_{LOAD}$ = 100pF,<br>$R_{LOAD}$ = 100k $\Omega$              |         | 5                                        | μs    |

| т                   | Zero Crossing Delay Time (Note 6) | $I_{DIFF} = 5\mu A \text{ pk-pk}, F_{VRS} = 200 \text{Hz}$                |         | 1                                        | ms    |

| T <sub>DELAY</sub>  |                                   | $I_{DIFF} = 50\mu A \text{ pk-pk}, F_{VRS} = 2.5 \text{KHz}$              |         | 10                                       | μs    |

| F <sub>MAX</sub>    | Maximum VRS Frequency             | $C_{LOAD} = 100 pF, R_{LOAD} = 100 K\Omega$<br>$I_{DIFF} = 5 \mu A pk-pk$ |         |                                          | KHz   |

| Electronic          | Timing Interface                  | ·                                                                         |         | L                                        |       |

| T <sub>RISE</sub> 1 | Sx Output Rise Time               | Sx Rises10% to 90%                                                        |         |                                          |       |

|                     |                                   | $C_{LOAD} = 6.8 nF, R_{LOAD} = 10 K\Omega$                                |         | 5                                        | μs    |

|                     |                                   | $C_{LOAD} = 12.7 nF, R_{LOAD} = 10 K\Omega$                               |         | 8                                        | μs    |

| T <sub>FALL</sub> 1 | Sx Output Fall Time               | Sx Falls 90% to 10%                                                       |         |                                          |       |

|                     |                                   | $C_{LOAD} = 6.8 nF, R_{LOAD} = 10 K\Omega$                                |         | 15                                       | μs    |

|                     |                                   | $C_{LOAD} = 12.7 nF, R_{LOAD} = 10 K\Omega$                               |         | 25                                       | μs    |

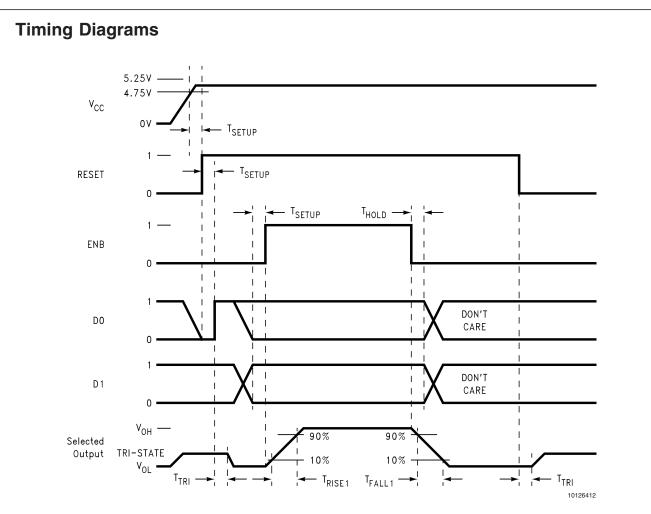

| T <sub>SETUP</sub>  | SetupTime (Notes 7, 8 and 9)      |                                                                           | 1       |                                          | μs    |

| T <sub>HOLD</sub>   | Hold Time                         |                                                                           | 0.5     |                                          | μs    |

#### AC Electrical Characteristics (Continued)

The following specifications apply for  $V_{CC} = 5V$ ,  $V_{S_{-HI}} = V_{CC}$ ,  $V_{RESET} = V_{CC}$ ,  $-40^{\circ}C \le T_A \le +125^{\circ}C$ . The AC Timing Characteristics are not production tested. Minimum and Maximum limits are guaranteed by device characterization.

| Symbol               | Parameter            | Conditions                                                | Minimum | Maximum | Units |

|----------------------|----------------------|-----------------------------------------------------------|---------|---------|-------|

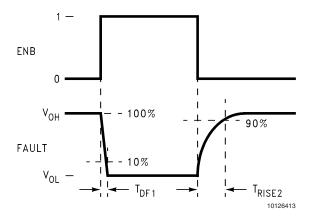

| T <sub>DF</sub> 1    | Fault Delay Time     | Sx Output Short to Ground Fault                           |         |         |       |

|                      |                      | From ENB = 1 to FAULT $\leq 10\%$                         |         |         |       |

|                      |                      | C <sub>FAULT</sub> = 25pF                                 |         | 2       | μs    |

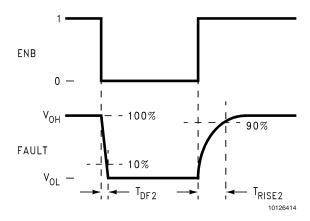

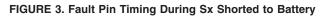

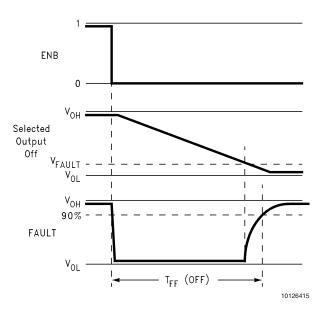

| T <sub>DF</sub> 2    | Fault Delay Time     | Sx Output Short to Battery Fault                          |         |         |       |

|                      |                      | From ENB = 0 to FAULT $\leq 10\%$                         |         |         |       |

|                      |                      | C <sub>FAULT</sub> = 25pF                                 |         | 2       | μs    |

| T <sub>TRI</sub>     | TRI-STATE Delay Time | From RESET = 0 to All Sx Outputs<br>Off                   |         | 2       | μs    |

| T <sub>RISE</sub> 2  | Fault Pin Rise Time  | 10% to 90%, C <sub>FAULT</sub> = 25pF                     |         | 5       | μs    |

| T <sub>FF(OFF)</sub> | False Fault Time     | From ENB = 0 to FAULT $\ge$ 90%                           |         |         |       |

| . ,                  |                      | C <sub>FAULT</sub> = 25pF                                 |         |         |       |

|                      |                      | $C_{LOAD} = 6.8 nF, R_{LOAD} = 10 K\Omega$                |         | 25      | μs    |

|                      |                      | $C_{LOAD} = 12.7 nF, R_{LOAD} = 10 K\Omega$               |         | 30      | μs    |

| T <sub>FF(ON)</sub>  | False Fault Time     | From ENB = 1 to FAULT $\ge$ 90%                           |         |         |       |

|                      |                      | C <sub>FAULT</sub> = 25pF                                 |         |         |       |

|                      |                      | $C_{LOAD} = 6.8$ nF, $R_{LOAD} = 10$ K $\Omega$           |         | 8       | μs    |

|                      |                      | $C_{LOAD} = 12.7 nF, R_{LOAD} = 10 K\Omega$               |         | 10      | μs    |

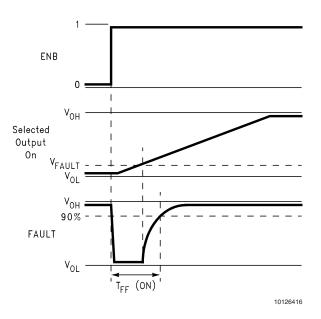

| T <sub>UDF</sub>     | Undefined Fault Time | From ENB = 0 for 8uSec, to Valid                          |         |         |       |

|                      |                      | FAULT                                                     |         |         |       |

|                      |                      | $C_{LOAD} = 6.8 nF, R_{LOAD} = 10 K\Omega$                |         | 20      | μs    |

|                      |                      | $C_{LOAD} = 12.7 \text{nF}, R_{LOAD} = 10 \text{K}\Omega$ |         | 25      | μs    |

Note 1: Absolute Maximum Ratings indicate the limits beyond which damage may occur.

**Note 2:** ESD Ratings is with Human Body Model: 100pF discharged through a  $1500\Omega$  resistor.

Note 3: Operating ratings indicate conditions for which the device is intended to be functional, but may not meet the guaranteed specific performance limits. For guaranteed specifications and conditions, see the Electrical Characteristics.

Note 4: Tested per VR Sensor Interface test circuit. See Figure 8 and Figure 9.

Note 5: Minimum Detect Current is not production tested at +85C. Specifications is guaranteed through device characterization and Test Limits at 25°C and 125°C.

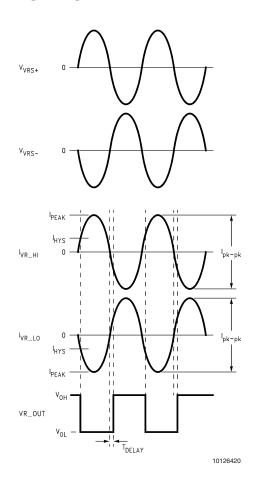

Note 6: VR Sensor Interface Tdelay, measured from VR input sine wave zero-crossing to VR\_OUT going high. See Figure 9.

Note 7: Electronic Timing Interface Tsetup, minimum time between Vcc > 4.75V and RESET = 1.

**Note 8:** Electronic Timing Interface Tsetup, minimum time between RESET = 1 and D0 = 1.

Note 9: Electronic Timing Interface Tsetup, minimum time between D0 / D1 = valid and ENB = 1.

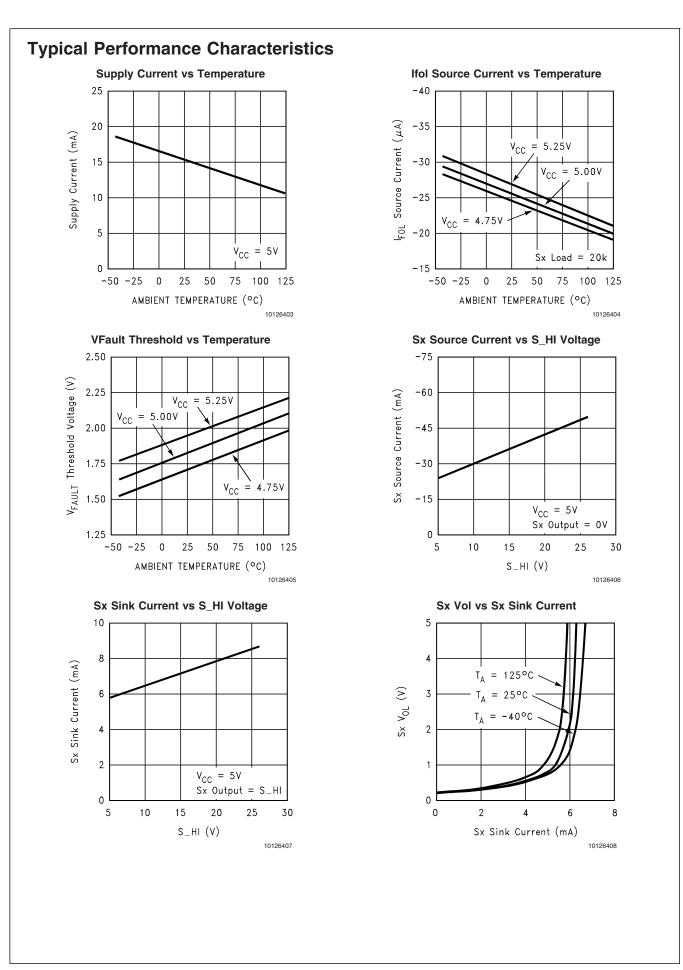

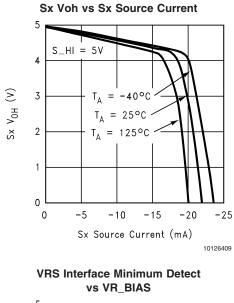

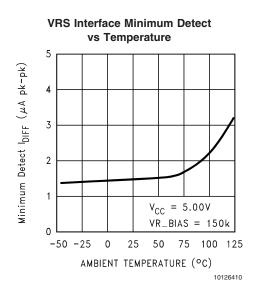

## Typical Performance Characteristics (Continued)

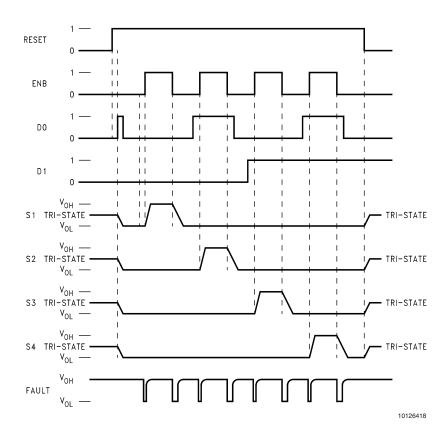

FIGURE 1. Electronic Timing Interface Timing Diagram

FIGURE 2. Fault Pin Timing During Sx Shorted to Ground

FIGURE 4. False FAULT Time for Disabled Sx Output

FIGURE 5. False FAULT Time for Enabled Sx Output

FIGURE 6. Time for Valid Fault Detection

FIGURE 7. Electronic Timing Interface Typical Waveforms

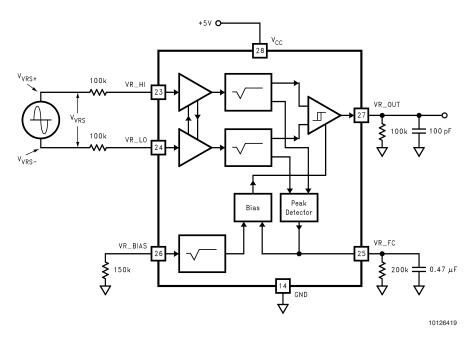

FIGURE 8. VR Interface Test Circuit

FIGURE 9. VR Interface Timing Diagram

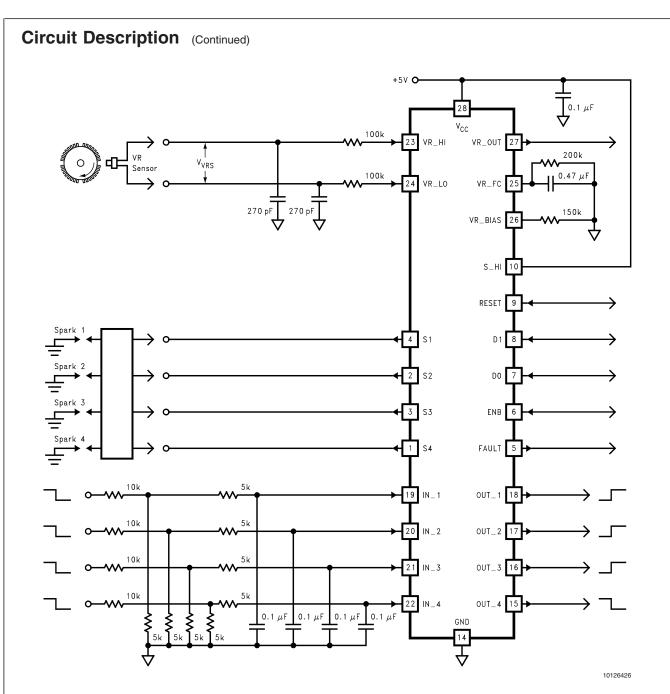

#### **Circuit Description**

#### **VR SENSOR INTERFACE**

The differential inputs, VR\_HI and VR\_LO are low impedance inputs with a DC voltage bias of one half of Vcc, Both inputs require equal value series resistance on their respective pins to convert the VR sensor voltage to a differential input current. The differential input current range is typically 2.5µA peak-to-peak to 2.5mA peak-to-peak. Each input has active current limiting that will clamp the current at typically +/-5mA. This is intended for short circuit protection and not for input signal limiting.

FIGURE 10. VR Sensor Interface Block Diagram

Differential voltages of 500mV peak-to-peak to 500V peakto-peak can be processed with the specified 100K $\Omega$  series resistor on each input. Numerous variables will determine the output voltage signal from a VR sensor across a frequency range. The input resistors can be scaled from typically 50K $\Omega$  to 200K $\Omega$  to keep the differential input current with-in the recommended range for a given VR Sensor output voltage. Bypass capacitors can be added to form a low pass filter to limit the differential input signal at the higher frequencies.

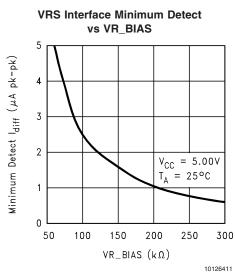

The VR Sensor interface utilizes a dynamic hysteresis which will increase the hysteresis level as the input signal from the VR Sensor increases. The circuit requires two external components to fully implement the hysteresis function: a capacitor on VR\_FC to filter and store the peak detector signals; and a 150K $\Omega$  resistor on VR\_BIAS to set a reference current for the hysteresis circuit. The typical value range for the peak detector storage capacitor is 0.1µF to 0.47µF.

The peak detector has an internal  $3K\Omega$  (typical) current limiting resistor to Vcc for charging the storage capacitor. An external resistor in parallel with the peak detector storage capacitor is used to set the RC discharge rate of the peak detector capacitor.

For input levels greater than typically 10µA peak-to-peak the voltage on the peak detector output pin VR\_FC is used to actively derive the hysteresis level. The active hysteresis will typically be 30% of the peak input signal. As the input level falls below typically 10µA peak-to-peak the hysteresis level will begin to rise as the static hysteresis level takes effect. The static hysteresis level is set by the current out of the VR\_BIAS pin and is a constant level of typically 1µA peak with a VR\_BIAS resistor of 150K $\Omega$ . This static hysteresis level acts as the minimum detect threshold as there will be no output if the input signal is not greater than the static hysteresis level.

The VR\_BIAS resistor can be scaled from typically 50K $\Omega$  to 500K $\Omega$ , but the practical range is typically 75K $\Omega$  to 300K $\Omega$ . Increasing the resistance (i.e. reducing the current) will lower the minimum hysteresis level. Conversely, reducing the resistance will raise the minimum hysteresis level. Since the VR\_BIAS current is modified by the same square root circuit used for the input signal, the relationship between the VR\_BIAS resistor value and the minimum detect level is not

www.national.com

#### Circuit Description (Continued)

linear. For VR\_BIAS values greater than  $500K\Omega$ , the minimum detect level is typically determined more by the internal device offsets, and thermal effects.

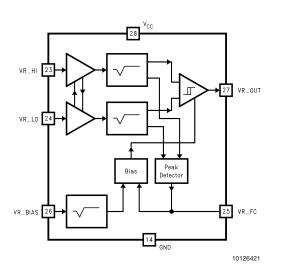

FIGURE 11. Voltage Comparator Block Diagram

#### **VOLTAGE COMPARATORS**

The circuit includes four general purpose voltage comparators that use an internal reference voltage to set their voltage thresholds. Three of the comparators have their noninverting inputs tied to the internal reference voltage, and their inverting-inputs are brought out. The remaining one comparator has its inverting input tied to the internal voltage reference, and its non-inverting input is brought out. All four comparators include hysteresis to improve noise immunity. The comparator outputs are internally pulled up to  $V_{\rm CC}$ . Any un-used comparator should have its input connected to device ground.

FIGURE 12. Electronic Timing Interface Block Diagram

#### Circuit Description (Continued)

|   |        |     |    |    | ining interne |     |     |     |

|---|--------|-----|----|----|---------------|-----|-----|-----|

|   | Inputs |     |    |    | Output        |     |     |     |

|   | RESET  | ENB | D0 | D1 | S1            | S2  | S3  | S4  |

|   | 0      | Х   | Х  | Х  | Tri           | Tri | Tri | Tri |

|   | 1      | 0   | Х  | Х  | L             | L   | L   | L   |

|   | 1      | 1   | 0  | 0  | Н             | L   | L   | L   |

| [ | 1      | 1   | 1  | 0  | L             | Н   | L   | L   |

|   | 1      | 1   | 0  | 1  | L             | L   | Н   | L   |

|   | 1      | 1   | 1  | 1  | L             | L   | L   | Н   |

**Electronic Timing Interface**

The Electronic Timing Interface provide signals to the spark module from the micro-processor. The interface requires four input data signals, and provides four output control channels.

The interface also provides one output channel for diagnostic information for any open or shorted loads on S1 to S4. The RESET pin has an internal pull-up resistor to V<sub>CC</sub> of typically 100K $\Omega$ , and the ENB pin has an internal pull-down resistor to ground of typically 100K $\Omega$ .

To put the outputs into the TRI-STATE mode at power-on, the RESET pin should be held low until V<sub>CC</sub> is above 4.75V. This can be accomplished by micro-processor control, or by adding a capacitor from the RESET pin to ground.

The RESET pin is used to disable the spark driver outputs by putting them in a TRI-STATE mode. While in the TRI-STATE mode the Open Output Fault detection circuitry is active. An open Output is detected by forcing a small current ( $I_{FOL}$ ) through the outputs to the loads, and monitoring the voltage on the output pins rises above the Output Fault Threshold Voltage ( $V_{FAULT}$ ) the FAULT pin will be forced low. The intent is to detect an open wire condition, and not necessarily to detect a local resistance threshold.

Note that if any output has a Short to battery fault, the fault pin will go low during this TRI-STATE mode. The internal comparator is unable to discern why an output pin may be above the Fault Threshold Voltage, only that it is. In any case, a fault is reported, even if it is not the anticipated fault.

The TRI-STATE mode is a latched condition. For the outputs to come out of the TRI-STATE mode, the RESET pin must be high, and then the data input pin D0 must toggle from a low state to a high state. The state of the outputs will now be set by the data inputs D0 and D1, and the ENB input. If ENB is low when the TRI-STATE mode is cleared, all of the outputs will go low.

Pins D0 and D1 are used select an output, and ENB will enable the selected output. The outputs have have active pull up to S\_HI, and the active pull down to Ground. The default not enabled output conditions is low, and the enabled output condition is high. Only one output can be enabled (high) at a time. The outputs are not latched in any state and will follow the input selected with D0 and D1 as long as ENB is high.

The detection of an output shorted to ground, or battery, is dependent on the status of ENB. While ENB is logical 0, all of the outputs are forced low and the Short to Battery fault detection circuitry is active. A Short to Battery is detected by monitoring the voltage on the output pins. If the voltage on any output pin is above the Fault Threshold Voltage ( $V_{FAULT}$ ) the FAULT pin will go low. The output current sink is limited to typically 8mA. The short to battery condition must be able to provide enough current to overcome the current limit and raise the output pin voltage above the  $V_{FAULT}$  threshold.

When ENB is logical 1, the selected output will be high and the Short to Ground detection circuitry is active. A Short to Ground is detected by monitoring the voltage on the output pins. If the voltage on the selected output pin is below the Fault Threshold Voltage ( $V_{FAULT}$ ) the FAULT pin will go low. The output current source is from S\_HI limited to typically 25mA to 50mA across the S\_HI voltage range. The short to ground condition must be allow enough resistance to allow the output pin voltage to fall below the  $V_{FAULT}$  threshold with the output sourcing short circuit current. Typically, a short to ground which has 100 Ohms of resistance, or more, can not be reliably detected. Typically, a short to ground of 20 Ohms, or less, can be reliably detected across the entire S\_HI voltage range and device operating temperature range. Note that if any output has a Short to Battery fault, a Short to

#### Circuit Description (Continued)

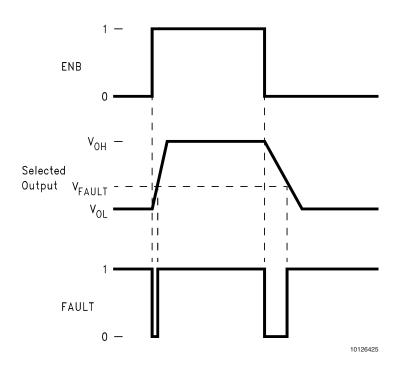

FIGURE 15. FAULT Pin Output During Normal Operation

Ground cannot be detected. The internal logic is unable to discern which output pin is above the Fault Threshold Voltage, only that a pin is. Thus, the logical requirement of an Sx pin voltage above the Fault Threshold voltage is met and no fault is reported.

The output rise and fall times are basically a function of the output current drive (source and sink) and the output load characteristics. Due to the scaling of the output stages, and variations in the value of S\_HI, the fall time will typically be two to ten times longer than the rise time for a given capacitive load.

Since the output fault detection mode changes immediately with the status of the ENB pin, and the voltage on the output

pin cannot change instantly, the FAULT pin will go low during the output transition times. The FAULT pin will stay low until the output voltage rises above, or falls below, the active fault threshold. See *Figure 15*.

When switching the outputs from the active mode to the TRI-STATE mode the ENB should be taken low first. This will take all of the outputs low. Then the RESET pin can be taken low. This will eliminate false 'open' faults that will be generated while waiting for the one output that was high, to discharge any capacitance below the  $V_{FAULT}$  threshold.

FIGURE 16. Typical Application

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.